接(3)

測試模組

(4)程式碼和測試模組之說明

1位元全加器邏輯閘層寫法

module fulladder_1(a,b,Cin,Sum,Cout);

//模組名稱宣告跟線路宣告 其中module類似C語言之{

input a,b,Cin;

//輸入線路宣告

output Sum,Cout;

//輸出線路宣告

wire d,e,f;

//資料型態線之宣告

xor(d,a,b);

//邏輯閘宣告,輸出為d,輸入為a,b

and(e,a,b);

//邏輯閘宣告,輸出為e,輸入為a,b

xor(Sum,d,Cin);

//邏輯閘宣告,輸出為Sum,輸入為d,Cin

and(f,d,Cin);

//邏輯閘宣告,輸出為f,輸入為d,Cin

or(Cout,f,e);

//邏輯閘宣告,輸出為Cout,輸入為f,e

endmodule

//程式結束 類似C語言}

1位元全加器資料處理層寫法

module fulladder_1(a,b,Cin,Sum,Cout);

//模組名稱宣告跟線路宣告 其中module類似C語言之{

input a,b,Cin;

//輸入線路宣告

output Sum,Cout;

//輸出線路宣告

assign {Cout,Sum}=a+b+Cin;

//assign指定敘述之意為資料處理層關鍵字,其中Cout為高位元,Sum為低位元

endmodule

//程式結束 類似C語言}

1位元全加器階層式寫法

module fulladder(a,b,Cin,Sum,Cout);

//模組名稱宣告跟線路宣告 其中module類似C語言之{

input a,b,Cin;

//輸入線路宣告

output Sum,Cout;

//輸出線路宣告

wire d,e,f;

//資料型態線之宣告

halfadder h1(a,b,d,e);

//類似C語言函式呼叫,呼叫出低階層半加器,並且命名為h1

halfadder h2(d,Cin,Sum,f);

//類似C語言函式呼叫,呼叫出低階層半加器,並且命名為h2

or(Cout,f,e);

//邏輯閘宣告,輸出為Cout,輸入為f,e

endmodule

//程式結束 類似C語言}

module halfadder(a,b,Sum,Cout);

//模組名稱宣告跟線路宣告 其中module類似C語言之{

input a,b;

//輸入線路宣告

output Sum,Cout;

//輸出線路宣告

xor(Sum,a,b);

//邏輯閘宣告,輸出為Sum,輸入為a,b

and(Cout,a,b);

//邏輯閘宣告,輸出為Cout,輸入為a,b

endmodule

//程式結束 類似C語言}

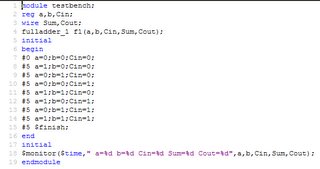

1位元全加器測試模組

module testbench;

//測試模組名稱宣告

reg a,b,Cin;

//宣告資料型態為暫存器線路,為了穩定訊號

wire Sum,Cout;

//宣告資料型態為一般線路

fulladder_1 f1(a,b,Cin,Sum,Cout);

//類似C語言函式之呼叫,並且命名此加法器名稱為f1

initial

//關鍵字,其之功能是按照順序1個1個輸入

begin

//類似C語言之{

#0 a=0;b=0;Cin=0;

//時間0 輸入訊號

#5 a=1;b=0;Cin=0;

//再隔5個時間單位 輸入訊號

#5 a=0;b=1;Cin=0;

//又再隔5個時間單位 輸入訊號

#5 a=0;b=0;Cin=1;

#5 a=1;b=1;Cin=0;

#5 a=1;b=0;Cin=1;

#5 a=0;b=1;Cin=1;

#5 a=1;b=1;Cin=1;

#5 $finish;

//測試終止結束之識別字

end

//類似C語言之}

initial

$monitor($time," a=%d b=%d Cin=%d Sum=%d Cout=%d",a,b,Cin,Sum,Cout);

//類似做C語言printf之工作 列印出時間

endmodule

//程式結束 類似C語言}

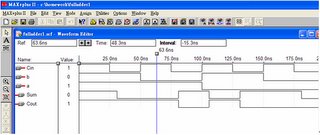

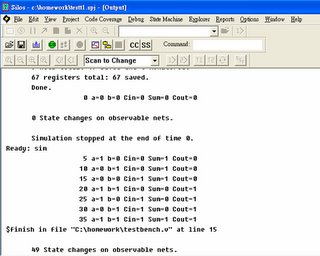

(5)結果和討論

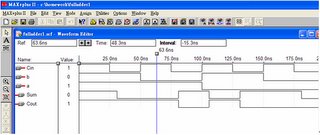

MAX+plus2波型圖

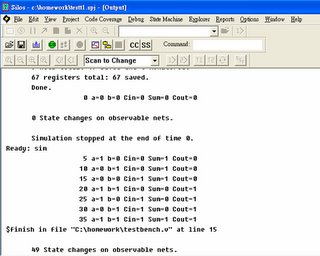

silos測試之結果

討論:

由波型圖跟測試模組得知結果為正確,舉個例子來看,像是第0秒時輸入a=0,b=0,Cin=0 則輸出為Sum=0,Cout=0就為正確,因為Sum=a+b+Cin,0=0+0+0,而其中Cin為輸入之進位,而Cout為輸出進位之數,在看幾組例子第5秒a=1,b=0,Cin=0,Sum=1+0+0,而且無輸出之進位,所以Sum=1,Cout=0,第20秒Sum=1+1+0此時造成進位而原位變成0,所以Sum=0,Cout=1,第35秒時Sum=1+1+1此時造成進位而原位又為1,因此Sum=1,Cout=1,以上亦可套用在波型圖上得知結果正確~